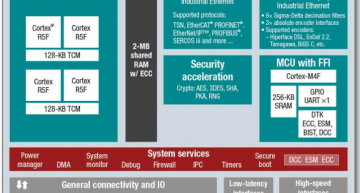

Intel has developed a soft IP microcontroller core for its FPGAs using the oipen source RISV-V instruction set

The Nios V processor is the next generation of soft processor for Intel’s Cycline, Stratix and Aria FPGAs based on the open-source RISC-V Instruction Set Architecture. This processor is available in the Intel Quartus Prime Pro Edition Software starting with version 21.3. This follows the 32bit Nios II, launched over a decade ago by Altera in Quartus 8.

The Nios V is based on RISC-V: RV32IA architecture designed for performance, with atomic extensions, 5-stage pipeline, and AXI4 interfaces.

The first version is the Nios V/m microcontroller. This has a benchmark performance of 0.46 DMIPS/MHz and 16 CoreMarks, making it about half the performance of an ARM M0+ core but comparable to other RV32 implementations. The benchmarking is perhaps less relevant as instruction extensions can be added in the FPGA fabric to boost performance for specific applications.

Intel is working on a general purpose application class processor called the Nios V/g to run operating systems such as Linux, presumably with a memory management unit.

Related articles

- RISC-V FPGA SoM module starts production

- €8m project for Europe's first RISC-V supercomputer chip

- Intel offers $2bn for RISC-V pioneer SiFive says report

- Codasip looks to hire 100 RISC-V engineers in UK.

Other articles on eeNews Europe

- II-VI boosts production at UK fab

- ST, Rosenberger team for 60GHz connector replacement

- European standards group for 6G metamaterial antenna technology

- World’s first quantum metro network in London

- Analysis shows coming over capacity for product types

- EU-US tech council to head off trade war

- Farewell Cree as it transitions to Wolfspeed